運算放大器和比較器

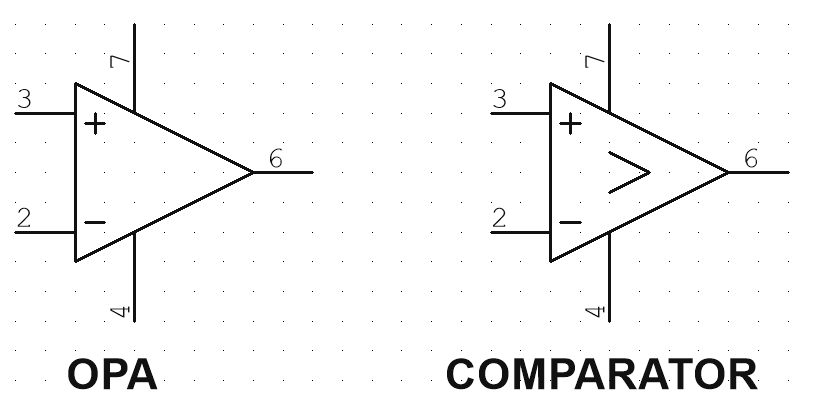

比較器和運算放大器電氣符號非常相像,都是有反相、同相兩(liang) 個(ge) 輸入端和一個(ge) 輸出端的器件,輸出端的輸出電壓範圍一般在供電的軌到軌之間;同時比較器和運算放大器都具有低偏置電壓、高增益和高共模抑製比的特點。

圖1 運算放大器和比較器

運算放大器和比較器的區別

①輸出:

比較器一般為(wei) 邏輯輸出,表征兩(liang) 個(ge) 輸入端的電位高低。現在市麵上大部分比較器的輸出都可以兼容TTL和CMOS,比較器的輸出始終為(wei) 正負電源軌之一。但是運算放大器的輸出是模擬信號,目前CMOS型的運放輸出一般都能做到軌到軌輸出【1】,運放的輸出電壓信號可以是接近正負電源軌之間的任意值。在運算放大器輸出動態範圍不超過後端邏輯電路的供電軌條件下,運放是可以用作比較器的。

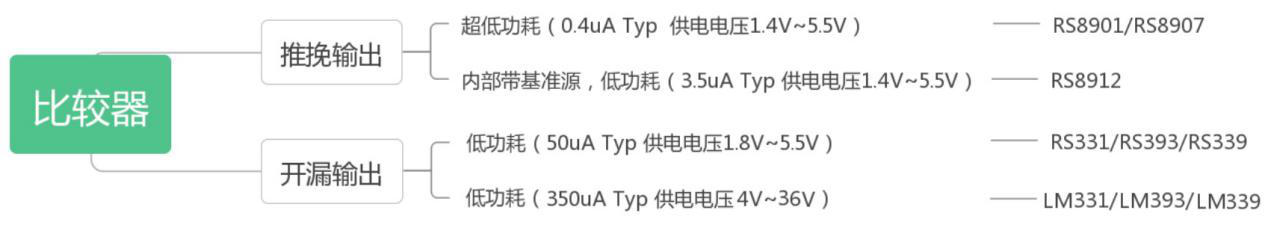

運放用作比較器時,輸出是推挽架構;而比較器可以做成推挽架構,也可以做成開漏輸出架構。

②速度

比較器適用於(yu) 開環係統,高速條件下工作,通常比較穩定。運算放大器過驅時可能會(hui) 飽和,使得恢複速度相對較慢,而比較器的過載恢複時間很短。

③輸入考慮因素:

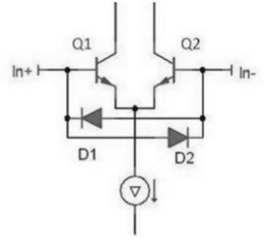

很多運算放大器都內(nei) 置保護電路,以防止大電壓損壞芯片。當輸入較大差分電壓時,很多運算放大器的輸入級都會(hui) 出現異常,因為(wei) 運算放大器的差分輸入電壓範圍通常是有限製的。

圖2 運放內(nei) 部輸入保護電路

非軌對軌運放的共模輸入電壓範圍,不能到正電源軌;而比較器是支持到正電源軌的。

運放用作比較器的應用場景

運放和比較器有很多相似的參數,在要求低失調電壓、低失調電流、高共模抑製的應用場景中選擇運放替代比較器是比較方便的。

運放一般有單運放,雙運放和四運放的封裝。將運放用作比較器,用一顆雙運放或者四運放就可以完成信號放大加比較的功能。無論是在便捷性、成本還是電路板的體(ti) 積上,都會(hui) 更有優(you) 勢。

運放用做比較器的缺點

從(cong) 辯證的角度來看,有優(you) 點就一定會(hui) 有缺點。在前文的區別中,我們(men) 已經提及到了運放和比較器的速度上的差異。因此在運放用作比較器時,需要重點關(guan) 注速度、差分輸入電壓範圍和放大器輸出是否過載這幾點。

運放作比較器的注意事項

①電源:

如果邏輯和運算放大器共用同一電源,軌到軌運算放大器可以驅動CMOS和TTL邏輯,但運算放大器與(yu) 邏輯電路如果不共用電源,則需要另外做接口電路。

②輸入阻抗和偏置電流:

運放用作比較器時,首先要滿足高輸入阻抗條件。CMOS運放這種電壓反饋運算放大器的輸入阻抗都在兆歐級別,滿足應用。而對於(yu) 電流反饋(跨導)運算放大器來說,反相輸入端阻抗極低,不能用作比較器。

③差分輸入特性

運算放大器的設計初衷是與(yu) 負反饋配合,盡可能地降低差分輸入。在具體(ti) 的應用中應結合實際需要的差分輸入電壓、與(yu) 運放實際能提供的最大差分輸入電壓來考慮。

④共模輸入特性

對於(yu) 老式的FET型輸入運算放大器,當輸入超過器件允許的共模電壓範圍時,會(hui) 產(chan) 生相位翻轉。目前各個(ge) 廠家生產(chan) 的運放都通過各種手段盡量不讓運放出現相位翻轉的現象。如果實際的共模電壓範圍超過運放允許的輸入共模電壓範圍,需要實際驗證確認是否正常工作。

⑤穩定性

用作比較器的運放由於(yu) 外部沒有負反饋,開環增益非常高,因此,諸如PCB的寄生電容,同相輸入端的對地阻抗都可能會(hui) 引起放大器的輸出震蕩,在設計上要重點考慮。

備注:

【1】CMOS 架構的運放在低電流輸出時,飽和壓降非常小,甚至隻有幾mV,輸出可以非常接近兩(liang) 個(ge) 電源軌,而不是等於(yu) 。

【2】18luck新利在线娱乐官网比較器選型樹狀圖

2020-03-03

2020-03-03